Latches

Contents

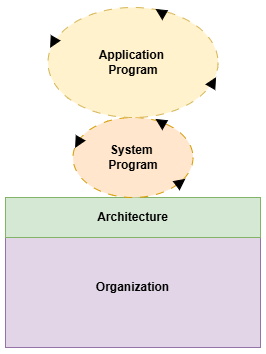

ToggleLatches form the simplest memory units in digital circuits, storing a single bit of data based on input levels until changed. These level-sensitive building blocks enable sequential logic, powering state machines, registers, and synchronization in everything from CPUs to microcontrollers.

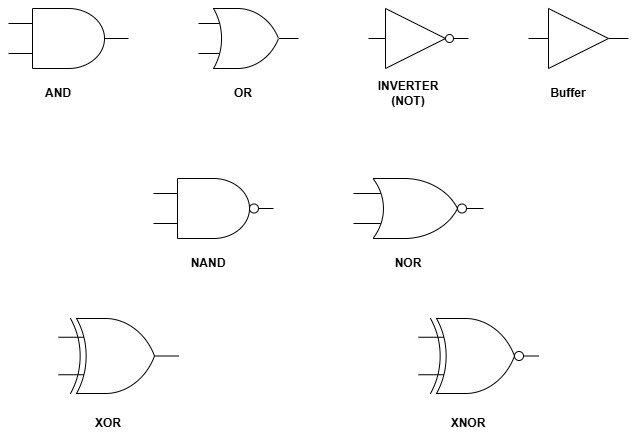

Built from basic gates like NAND or NOR, latches “remember” without clocks in their purest form, making them foundational for flip-flops and more complex storage. They bridge combinational gates to full sequential systems like those in Von Neumann ALUs. Think of a light switch that stays on until flipped—that’s a latch holding a state (0/1).

What Are Latches?

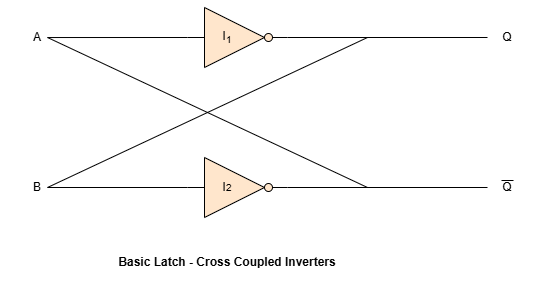

Latches are memory cells with two stable states (0 or 1), using feedback loops of gates to hold value. Unlike combinational circuits, outputs depend on past inputs via memory. They respond to input levels (high/low enable). These sequential circuits are called latches since one bit of information can be locked or latched. The basic latch consists of two inverters.

What is the Latching Effect?

The latching effect is the behavior where a latch remembers and holds its output even after the input signals are removed. This happens because of the feedback loop between the two gates inside the latch. That feedback continuously reinforces the current output, making the circuit bistable (two stable states).

Each gate’s output becomes the other gate’s input, so the circuit keeps itself stable.

Latches update immediately when inputs change, and when inputs return to the “inactive” state, the latch simply holds whatever value it had.

Purpose of Latches in Digital Systems

Latches temporarily store data, synchronize signals, and build stateful logic. Key roles include data buffering in pipelines, enabling transparent pass-through, and forming flip-flops for clocks. They handle asynchronous inputs gracefully, crucial for reset circuits or debouncing switches.

In processors, latches queue instructions before flip-flops. Without latches, sequential circuits couldn’t evolve states over time—your keyboard buffer uses them to latch keypresses smoothly. They simplify designs by providing level-controlled memory.

Types of Latches

- SR Latch

- D Latch

- JK Latch

- T Latch

Advantages

Simplicity: Few gates (2-4), low cost/area.

Transparency: D latch passes data continuously—great for pipelines.

Async Friendly: No clock skew, fast in simple designs.

Power Efficient: No clock toggling overhead.

Flexible: Build FFs, easy debouncing.

Disadvantages

Level-Sensitive Glitches: Transparent mode risks races if inputs glitch.

No Precise Timing: Enable overlap causes metastability.

Harder Scaling: Large systems prefer edge FFs for sync.

Invalid States: SR both-1 problem.

Timing Analysis Tough: Hazards in async feedback.